கற்றனைத்தூறும் அறிவு ...सिधिर भवती करमजा

How Bubble Memory Works - Link

Click HERE to see animations from Wiki Media to Understand How Bubble Memory Works

Charge Coupled Devices - CCD

Click HERE to download as a PDF

CCD Operation

A Charge Coupled Device (CCD) is

a highly sensitive photon detector. The CCD is divided up into a large number

of light-sensitive small areas (known as pixels) which can be used to build up

an image of a scene. A photon of light which falls within the area defined by

one of the pixels will be converted into one (or more) electrons and the number

of electrons collected will be directly proportional to the intensity of the

scene at each pixel. When the CCD is clocked out, the number of electrons in

each pixel is measured and the scene can be reconstructed.

The figure below shows a

simplified cross section through a CCD. The pixels are defined by the position

of electrodes above the CCD. If a positive voltage is applied to the electrode,

then this positive potential will attract all of the negatively charged

electrons close to the area under the electrode. In addition, any positively

charged holes will be repulsed from the area around the electrode. Consequently

a potential well will form in which the electrons produced by the incoming

photons will be stored.

As more and more light falls

onto the CCD, then the potential well surrounding this electrode will attract

more and more electrons until the potential well is full. To prevent this

happening the light must be prevented from falling onto the CCD for example, by

using a shutter as in a camera. Thus, an image can be made of an object by

opening the shutter, "integrating" for a length of time to fill up

most of the electrons in the potential well, and then closing the shutter to

ensure that the full well capacity is not exceeded.

An actual CCD will consist of a large number

of pixels (i.e., potential wells), arranged horizontally in rows and vertically

in columns. The number of rows and columns defines the CCD size, typical sizes

are 1024 pixels high by 1024 pixels wide. The resolution of the CCD is defined

by the size of the pixels, also by their separation (the pixel pitch).

CCD Operation

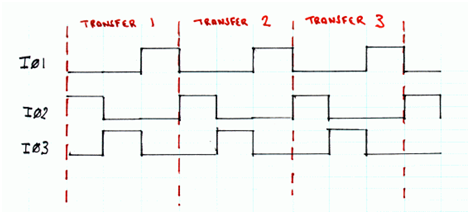

The figure below shows a cross

section through a row of a CCD. Each pixel consists of three electrodes IØ1,

IØ2, and IØ3. Only one of these electrodes is required to create the potential

well, but other electrodes are required to transfer the charge out of the CCD.

The upper section of the figure (section 1) shows charge being collected under

one of the electrodes. To transfer the charge out of the CCD, a new potential

well can be created by holding IØ3 high, the charge is now shared between IØ2

and IØ3 (section 2). If IØ2 is now taken low, the charge will be fully

transferred under electrode IØ3 (section 3). To continue clocking out the CCD,

taking IØ1 high and then taking IØ3 low will ensure that the charge cloud now

drifts across under the IØ1 electrodes. As this process is continued, the

charge cloud will progress either down the column, or across the row, depending

upon the orientation of the electrodes.

The figure below (clocking diagram) shows the progression under which each electrode is held high

and low to ensure that charge is transferred through the CCD.

Initially, IØ2 is high - usually

to around 12V, and the charge is held under that electrode as in (1)

previously. When IØ3 is held high, and IØ2 is taken low (usually 0 V), the

charge migrates under the IØ3 electrode (as in (2)). Finally, taking IØ1 high

and IØ3 low transfers the charge under IØ1 (as in (3)). This process is

repeated in transfer 2 and transfer 3, the charge has now been moved three

pixels along. This process is known as charge coupling (hence CCD).

For most of the CCD, the

electrodes in each pixel are arranged so that the charge is transferred

downwards along the columns. Hence, during the CCD clocking operation, rows are

transferred downwards to the final row (the readout register) which is used to

transfer the charge in each pixel out of the CCD so it can be measured.

In the read out register, the

electrodes are arranged so that the charge is transferred in the horizontal

direction, along the readout register.

The final process on the CCD is

the reading of each pixel so that the size of the associated charge cloud can

be measured. At the end of the readout register is an amplifier which measures

the value of each charge cloud and converts it into a voltage.

MOS Dynamic RAM Cell

Click HERE to download as PDF

Memory cells of a dynamic RAM memory consist of capacitor

storing electric charges hence logic voltage levels. A bit cell

constitutes a transistor with a capacitor interconnected to the line that

selects a memory row and to the bit line in the word (bit read and write

lines). The figure below shows such a bit cell based on a MOS FET.

A write takes place as

a result of row line selection (positive voltage) and insertion through a bit

line of the voltage that corresponds to the stored bit: 0 V for logical zero

and the positive voltage for one. For logical one, the capacitor will charge

through the conducting transistor to the positive voltage. For zero, the

transistor will be turned off and the condenser will discharge if loaded or it

will remain not charged (in both cases the condenser plate at the transistor

side will reach 0V potential).

On read, a row line will be set to the positive potential and

the transistor will be turned on. If the condenser was charged (the bit cell

was storing one), the positive voltage from the condenser plate will be

transferred into the bit line (readout of one) after which the capacitor

discharges through the bit line. If the capacitor was not charged, 0 V will be

transferred to the bit line i.e. a logical zero, stored in this cell. After

readout of a bit cell, the condenser has to be charged again to restore the

previous contents of the memory cell. It is done by execution of the read cycle

for the same information. A data-readout from dynamic RAM memory is destructive

and in this memory a read cycle is always followed by a write cycle.

A semiconductor dynamic RAM memory is a volatile memory,

since charged capacitors are subject to spontaneous discharging. The reason for

this is the leakage that results from impurities in the crystalline structure

of silicon. Therefore, dynamic RAM memory requires periodic refreshing of

stored data. This is done by special refresh circuits, which are always added

as an extension of the proper data storing circuitry.

MOS Dynamic RAM Cell – Refreshing Circuits

Click HERE to download as PDF

In

a MOS dynamic RAM cell data is stored as charge on a capacitor. As charge is continuously

leaked from the capacitor, the data stored (bit 1) will be lost if not being

refreshed from an external circuit. Such a circuit which constantly restores

the charge on a capacitor representing bit 1 is called a refresh circuit. A

basic refresh circuit shown in the following diagram is described below.

To enable refresh operation R/W

line, ROW line and REFRESH line are made HIGH. This turns ON transistor and

connects capacitor to COLUMN line. As R/W is HIGH, output buffer is

enabled and the stored data bit is applied to the input of refresh buffer. The

enabled refresh buffer then produces a voltage on COLUMN line corresponding to

the stored bit and thus replenishing the capacitor with charge.

This process is repeated at a particular frequency to ensure

that the 1 data bit stored in the cell is not lost due to leakage.

Atomic and Nuclear Physics - University Model Test - 7BPH4C1

Department of Physics - Dr.Zakir Husain College, Ilayangudi.

Atomic And Nuclear Physics –4BPH4C1

Time: 3 Hours Max Marks: 75

Part – A (10 x 2 = 20)

Answer All the Questions

2. Write note on photoelectric cell.

3. Give Pauli’s exclusion principle.

4. Define Bohr Magneton.

5. State Mosley’s Law.

6. What is a unit cell?

7. What are the limitations of cyclotron?

8. Define Half Life.

9. Write note on Van Allen Belts.

10.What are Baryons?

Part – B (5 x 5 = 25)

Answer All the Questions

11. Discuss Aston’s mass spectrograph and explain how isotopes are detected.

(OR)

Explain the theory of determining e/m of photo-electron using Lenard’s method.12. Explain the various quantum numbers associated with the vector atom model..

(OR)

Explain emission of D2 lines in sodium spectrum using term symbols and selection rules.13. State and derive Bragg’s law. Explain the working of Bragg spectrometer.

(OR)

Draw NaCl structure and discuss it.14. Explain how electrons are accelerated to very high energy by betatron.

(OR)

Write a note on thermo nuclear reactions15. Discuss the method of radio carbon dating.

(OR)

Explain latitude effect in cosmic rays.

Part – C (3 x 10 = 30)

Answer any three Questions

16. Explain Frank and Hertz Experiment to determine critical potential.

17. Describe Stern and Gerlach experiment and indicate the importance of the results obtained.

18. Describe the quantum treatment of normal Zeeman Effect.

19. Explain the construction and working of a GM counter.

20. Write an essay on the nuclear reactor

University Model Examination - Digital Electronics - 4BPH6C2

Part - A

1.Convert the decimal number 65.6 into hexadecimal.

2.State distributive laws of Boolean algebra.

3.Simplify the Boolean expression A(A+B+AB).

4.What is the difference between Karnaugh map and truth table.

5.What is meant by flip-flop?

6.How many flip-flops are required to construct a MOD-9 counter.

7.Write the equivalent analog voltage of (11011001)2 if the full scale voltage is 5 V.

8.Write note on resolution of an ADC.

9.What is the advantage of a PROM over ROM?

10.What is a magnetic bubble memory?

Part - B

11.(a) Describe the function of an AND gate with its truth table.

(OR)

(b)State and prove De Morgan's Theorem

12.(a) Explain the working of Half Adder.

(OR)

(b) Construct and simplify K-map for the expression f(A,B,C,D) = ∑(0,1,4,6,7,8,9,10,11,15).

13.(a) Describe the action of an RS flip-flop with neat circuit diagram and truth table.

(OR)

(b) Explain the working of Johnson counter.

14.(a) How does a simultaneous ADC operates?

(OR)

(b) Explain the counter type ADC.

15.(a) Explain the function of a MOS Static RAM cell.

(OR)

(b) Discuss the construction details of magnetic disc memories.

Part - C

16. Explain how NOR gate can be used a universal building block.

17. Explain the working of an 8421 BCD Binary adder.

18. With a neat diagram, explain the action of a 4-bit shift register.

19. Describe the working of a weighted registor type D/A converter.

20.What is a PROM? Explain how a PROM can be programmed with neat diagrams.

MOS Static RAM Cell

Click HERE to download as PDF

Static random access memory (SRAM) can retain its stored

information as long as power is supplied. This is in contrast to dynamic RAM

(DRAM) where periodic refreshes are necessary. The term ``random access'' means

that in an array of SRAM cells each cell can be read or written in any order,

no matter which cell was last accessed.

The structure of a 6 MOS FET SRAM cell, storing one bit of

information, is shown in the following figure.

The core of the cell is formed by two CMOS inverters, where

the output potential of each inverter (Vout) is

fed as input into the other (Vin).

This feedback loop stabilizes the inverters to their respective state.

The access transistors and the word and bit lines, WL and BL,

are used to read and write from or to the cell. In standby mode the word line

is low, turning the access transistors off. In this state the inverters are in

complementary state. When the p-channel MOSFET of the left inverter is turned

on, the potential Vl,out

is high and the p-channel MOSFET of inverter two is turned off, Vr,out is low.

To write information the data is imposed on the bit line and

the inverse data on the inverse bit line,.

As

the driver of the bit lines is much stronger it can assert the inverter

transistors. As soon as the information is stored in the inverters, the access

transistors can be turned off and the information in the inverter is preserved.

For reading the word line is turned on to activate the access

transistors while the information is sensed at the bit lines.

Programming Bipolar PROM

Click HERE to download as PDF

Programming Bipolar PROM

ROM stands for Programmable

Read Only Memory.

Unlike ordinary ROMs, which are programmed at the manufacturer’s site, PROMs

are programmed by the users.So, user can load a program into the PROM according to their own specifications. This is an advantage of PROM over ROM. They are also known as Write Once Memory (WOM).

PROM is made by connecting the address lines to the data lines by a decoder

with connections between decoder o/p lines and data lines made by bipolar

transistors with fuses at their emitters. To program the PROM appropriate fuse

links are flown by sending a high current pulse through the fuses. This process

is illustrated below using 2 address lines and 4 data line with a decoder

connecting them.

Initially the PROM from the manufacturer contains bipolar

transistor fuse links between decoder lines are all intact as shown in the following

schematic diagram.

In such a case, the output of all the

data lines is logic 1 irrespective of the address on the address line. At the

user site user can selectively flow the fuses by sending a high current pulse

through them leaving logic 0s at selected data lines for specific addresses. For an example, for the following diagram

shown with flown fuses the data read for all the possible addresses are given

in the table below.

ADDRESS

|

DATA

|

||||

A0

|

A1

|

D3

|

D2

|

D1

|

D0

|

0

|

0

|

0

|

1

|

0

|

0

|

0

|

1

|

0

|

1

|

0

|

1

|

1

|

0

|

1

|

0

|

0

|

1

|

1

|

1

|

0

|

0

|

1

|

0

|

The programming is done through a programmer called PROM

burner. Three technologies exist for making fusible links at the emitters of

bipolar transistors. They are nichrome metal links, poly silicon links and pn junction

links.

Resolution and Accuracy of an ADC

Resolution of an ADC:

Resolution of an ADC is defined as the smallest voltage increment corresponding to a 1 bit LSB change.It is the smallest analog voltage an ADC can resolve.

Accuracy of an ADC:

Accuracy of an ADC determines how close the actual digital output is to the theoretically expected digital output for a given analog input. The accuracy of an ADC is a function of its internal circuitry and noise from the external sources connected to the ADC.

Successive Approximation ADC

Click HERE to download as PDF

Successive Approximation type ADC is the most widely used and

popular ADC method. The conversion time is maintained constant in successive

approximation type ADC, and is proportional to the number of bits in the

digital output, unlike the counter and continuous type A/D converters. The

basic principle of this type of A/D converter is that the unknown analog input

voltage is approximated against an n-bit digital value by trying one bit at a

time, beginning with the MSB. The principle of successive approximation process

for a 4-bit conversion is explained here. This type of ADC operates by

successively dividing the voltage range by half, as explained in the following

steps.

(1) The MSB is initially set to 1 with the remaining three

bits set as 000. The digital equivalent voltage is compared with the unknown

analog input voltage.

(2) If the analog input voltage is higher than the digital

equivalent voltage, the MSB is retained as 1 and the second MSB is set to 1.

Otherwise, the MSB is set to 0 and the second MSB is set to 1. Comparison is

made as given in step (1) to decide whether to retain or reset the second MSB.

The above steps are more accurately illustrated with the help

of an example. Let us assume that the 4-bit ADC is used and the analog input

voltage is VA = 11 V. when the conversion starts, the MSB bit is set

to 1.

Now VA

= 11 V > VD = 8V = [1000]2

Since the unknown analog input voltage VA is

higher than the equivalent digital voltage VD, as discussed in step

(2), the MSB is retained as 1 and the next MSB bit is set to 1 as follows

VD = 12 V = [1100]2

VD = 12 V = [1100]2

Now VA = 11 V < VD

= 12 V = [1100]2

Here now, the unknown analog input voltage VA is

lower than the equivalent digital voltage VD. As discussed in step

(2), the second MSB is set to 0 and next MSB set to 1 as VD = 10 V = [1010]2

Now again VA = 11 V > VD = 10 V = [1010]2

Again as discussed in step (2) VA>VD,

hence the third MSB is retained to 1 and the last bit is set to 1. The new code

word is VD

= 11 V = [1011]2

Now finally VA = VD , and the conversion stops.

It consists of a successive approximation register (SAR), DAC

and comparator. The output of SAR is given to n-bit DAC. The equivalent analog

output voltage of DAC, VD is applied to the non-inverting input of

the comparator. The second input to the comparator is the unknown analog input

voltage VA. The output of the comparator is used to activate the

successive approximation logic of SAR.

When the start command is applied, the SAR sets the MSB to

logic 1 and other bits are made logic 0, so that the trial code becomes 1000.

Advantages:

1. Conversion time is very small.

2. Conversion time is constant and independent of the amplitude of the analog input signal VA.

1. Conversion time is very small.

2. Conversion time is constant and independent of the amplitude of the analog input signal VA.

Disadvantages:

1. Circuit is complex.

2. The conversion time is more compared to flash type ADC.

1. Circuit is complex.

2. The conversion time is more compared to flash type ADC.

Subscribe to:

Posts (Atom)